發(fā)布日期:2023-03-22 16:33 瀏覽次數(shù):

本標(biāo)準(zhǔn)規(guī)定了VHDL用于可編程邏輯器件軟件編程安全細(xì)則。

本標(biāo)準(zhǔn)適用于可編程邏輯器件軟件VHDL的編程安全設(shè)計(jì)、編碼、測(cè)試及其使用。ASIC數(shù)字電路設(shè)計(jì)時(shí)也可參照使用。

下列文件對(duì)于本文件的應(yīng)用是必不可少的。凡是注日期的引用文件,僅注日期的版本適用于本文件。凡是不注日期的引用文件,其最新版本(包括所有的修改單)適用于本文件。

GB/T 11457-2006 信息技術(shù) 軟件工程術(shù)語

GB/T 33781-2017 可編程邏輯器件軟件開發(fā)通用要求

GB/T 11457-2006和GB/T 33781-2017界定的術(shù)語和定義適用于本文件。

下列縮略語適用于本文件。

FPGA:現(xiàn)場(chǎng)可編程門陣列(Field Programmable Gate Array)

VHDL:超高速集成電路硬件描述語言(Very-high-speed integrated circuit Hardware Description Language)

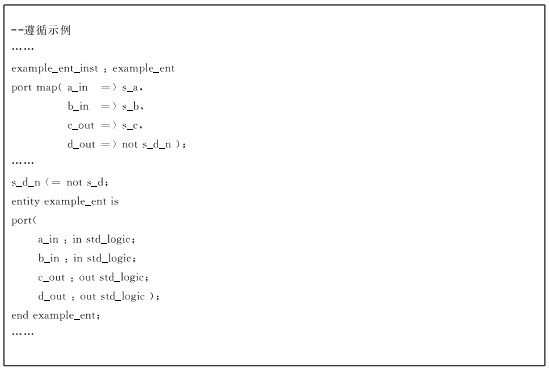

5.1 例化類

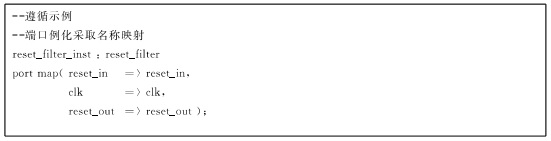

5.1.1 端口例化應(yīng)采取名稱映射的方式,避免位置映射。

在進(jìn)行端口例化時(shí),應(yīng)采取名稱映射的方式,避免位置映射,利于提高程序的可讀性和可維護(hù)性。

示例:

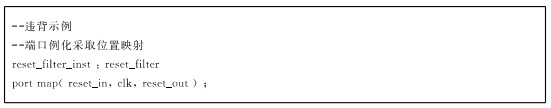

5.1.2 例化時(shí)不應(yīng)輸入端口懸空。

在進(jìn)行例化時(shí),輸入端口應(yīng)有確定的輸入關(guān)系,不應(yīng)懸空。

示例:

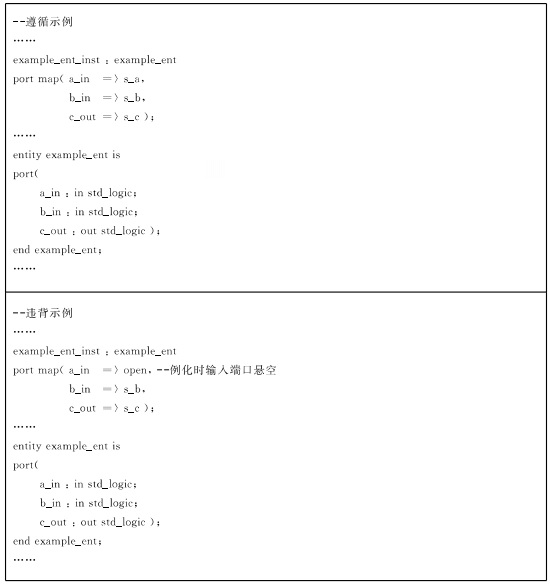

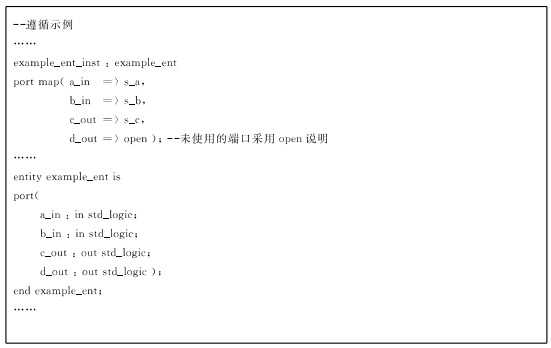

5.1.3 例化時(shí)未使用的輸出端口宜采用“openen”說明。

例化時(shí),如存在不需使用的輸出端口,宜采用“pen”說明。

示例:

5.1.4 端口例化時(shí)不應(yīng)進(jìn)行邏輯運(yùn)算操作。

以上為標(biāo)準(zhǔn)部分內(nèi)容,如需看標(biāo)準(zhǔn)全文,請(qǐng)到相關(guān)授權(quán)網(wǎng)站購買標(biāo)準(zhǔn)正版。